Phase Locked Loop (PLL)

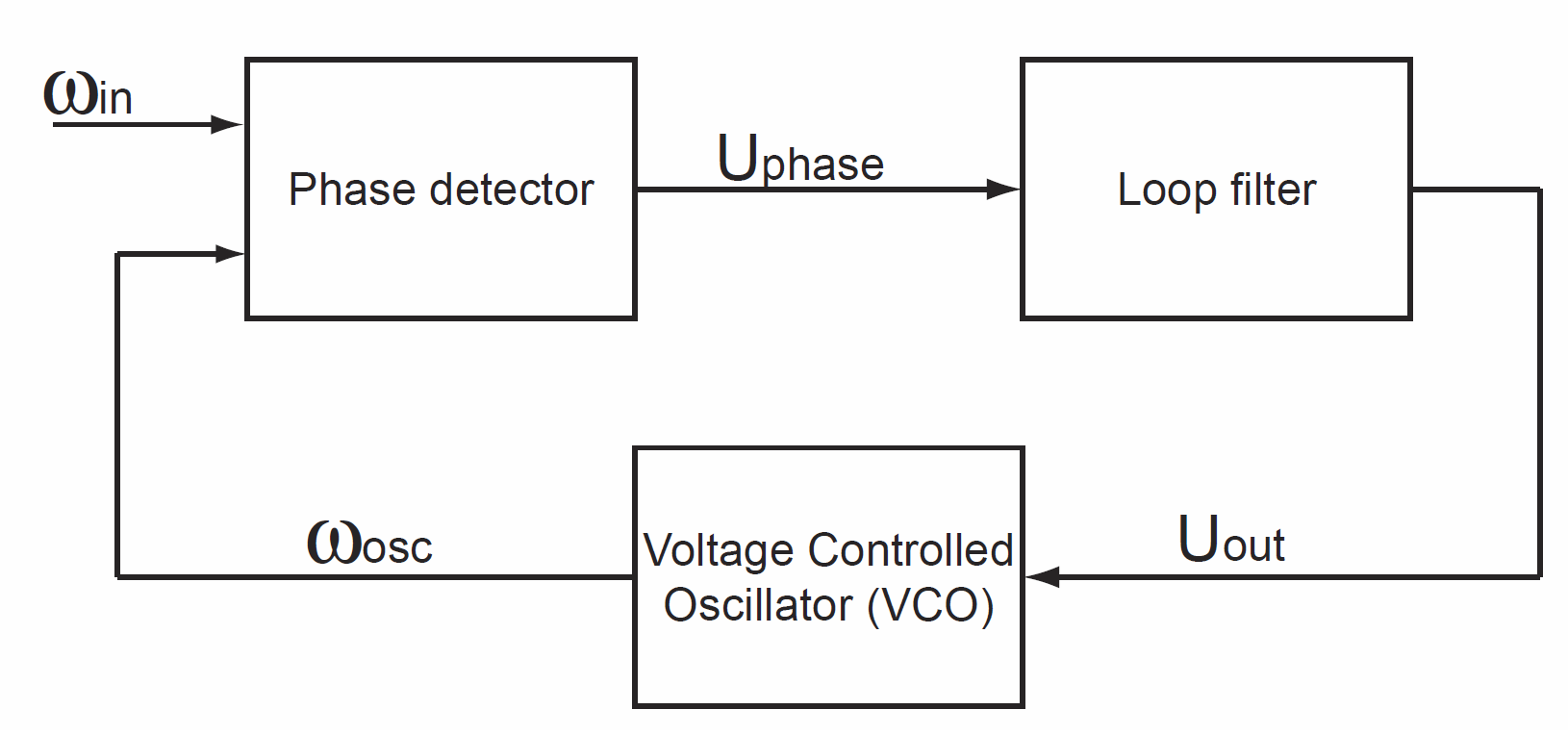

Im Transceiver ist eine PLL eingebaut, die für die Synchronisation der einzelnen Takte im Baustein dient. Ein Blockdiagramm, das die Funktionsweise der PLL zeigt, ist in Abb. 1 dargestellt.

Abbildung 1: Aufbau eines Koaxialkabels

Das Ziel der PLL ist es, die Frequenz \(\omega_{osc}\) an die Frequenz \(\omega_{in}\) anzugleichen. Der Frequenzunterschied wird durch einen Phasendetektor ermittelt, der eine Spannung \(U_{phase}\) linear zum Phasenunterschied \(\omega_{in}-\omega_{osc}\) liefert. Dieser Spannung \(U_{phase}\), die zunächst mittels des PLL Loop Filter angepasst wird, steuert einen „Voltage Controlled Oscillator (VCO)“. Ein VCO ist eine elektronische Schaltung, die eine periodische Spannung erzeugt. Die Frequenz der Spannung \(\omega_{osc}\) ist linear zur Eingangsspannung \(U_{out}\). Ist die Spannung \(U_{out}=0 V\), dann sind die Frequenzen \(\omega_{in}\) und \(\omega_{osc}\) identisch. Damit die Aufgabe des PLL Loop Filter verständlich wird, muss man wissen, wie die Phasendetektion funktioniert. Der Phasendetektor multipliziert die beiden Eingangssignale \(\omega_{in}\) und \(\omega_{osc}\) miteinander. Das bei der Multiplikation resultierende Signal \(U_{phase}\) ergibt sich somit zu:

wobei \(\Phi\) die Differenz zwischen \(\omega_{in}\) und \(\omega_{osc}\) beschreibt und \(K\) ein Verstärkungsfaktor ist. Werden die beiden Sinusfunktionen der oberen Gleichung miteinander multipliziert und beachtet man dabei das Additionstheorem

so entsteht folgender Term:

Wie bereits ersichtlich ist, entsteht bei der Multiplikation eine Schwingung mit der doppelten Frequenz \(\omega_{in}\). Die Aufgabe des “PLL Loop”-Filters ist es nun, die doppelte Frequenz aus dem Signal herauszufiltern (Tiefpass-Filter). Übrig bleibt eine Spannung \(\sin(\Phi t)\), die abhängig vom Frequenzunterschied ist. Für kleine Werte von \(\Phi \) ist:

Dies gilt natürlich nur, wenn \( \Phi \ge \frac{p}{2} \) ist. Ansonsten kann sich die PLL nicht synchronisieren. Dieser Bereich von \(0\) bis \(\frac{p}{2} \) wird Fangbereich genannt.

Die PLL im CC1020 ist abhängig von der Datenübertragungsrate. Insofern muss der “PLL Loop”-Filter bei jeder Übertragungsrate neu dimensioniert werden. Damit dies möglich ist, wird der Filter nicht im Baustein integriert, sondern muss extern aufgebaut werden. Um den Anwender nicht mit komplexen Filterberechnungen zu belasten hat der Hersteller für unterschiedliche Übertragungsraten Dimensionierungen angegeben. Die im Praktikum benutzten Module sind für Datenraten bis 9,6 kBit/s optimiert.