2. Verwendete Geräte

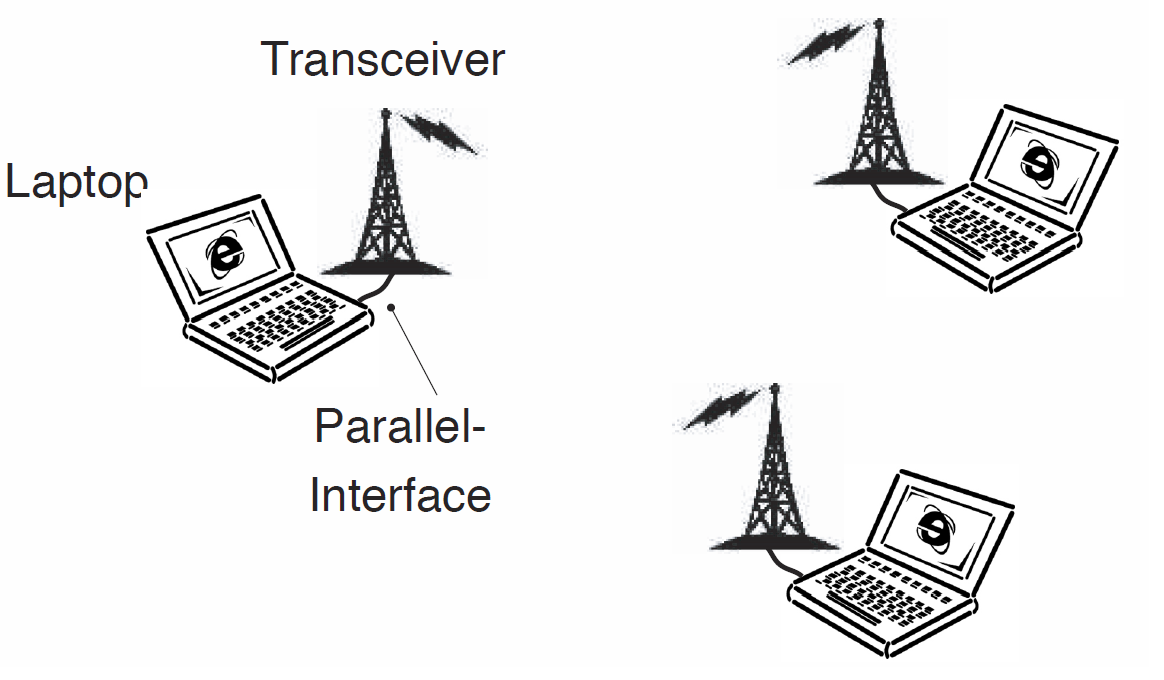

Für die Untersuchungen an der physikalischen Schicht stehen Transceiver der Firma Texas Instruments vom Typ CC1020 zur Verfügung. Diese Art von Transceiver gehört zur Familie der "Single Chip Low Power RF Transceiver for Narrow Band Systems" und operiert im 400 MHz-Bereich (US-Variante) und 800 MHz-Bereich (europäische Variante). In der Regel werden mindestens zwei Transceiver benötigt. Ein Transceiver wird als Sender verwendet und der andere Transceiver operiert als Empfänger. Kommunizieren mehr als zwei Transceiver miteinander, so bilden sie ein Netzwerk, wie es n Abb. 1-1 skizziert ist.

Wie in Abb. 1-1 zu sehen ist, wird ein Transceiver über die parallele Schnittstelle (Printer Interface) an einen Computer angeschlossen. Eine genauere Beschreibung der parallelen Schnittstelle ist Kapitel "Zusätzlich Literatur" zu entnehmen. Der Computer ist mit dem Betriebssystem Linux ausgestattet und verfügt über einen Treiber zur Steuerung des Transceivers. Pro Versuchsaufbau werden bis zu 2 Transceiver gleichzeitig verwendet. Da in einem Termin mehrere Versuchsaufbauten parallel betrieben werden, muss gewährleistet werden, dass sie sich nicht gegenseitig stören.

In den folgenden Abschnitten werden die einzelnen Komponenten der Transceiver beschrieben.

2.1 Transceiver CC1020

Der Transceiver bietet die Möglichkeit an, Daten drahtlos zu einem anderen Transceiver zu senden oder von einem entfernten Transceiver zu empfangen. Dafür besitzt ein Transceiver eine Vielzahl von Funktionsblöcken, die beim CC1020 in einer "single chip"-Lösung implementiert sind.

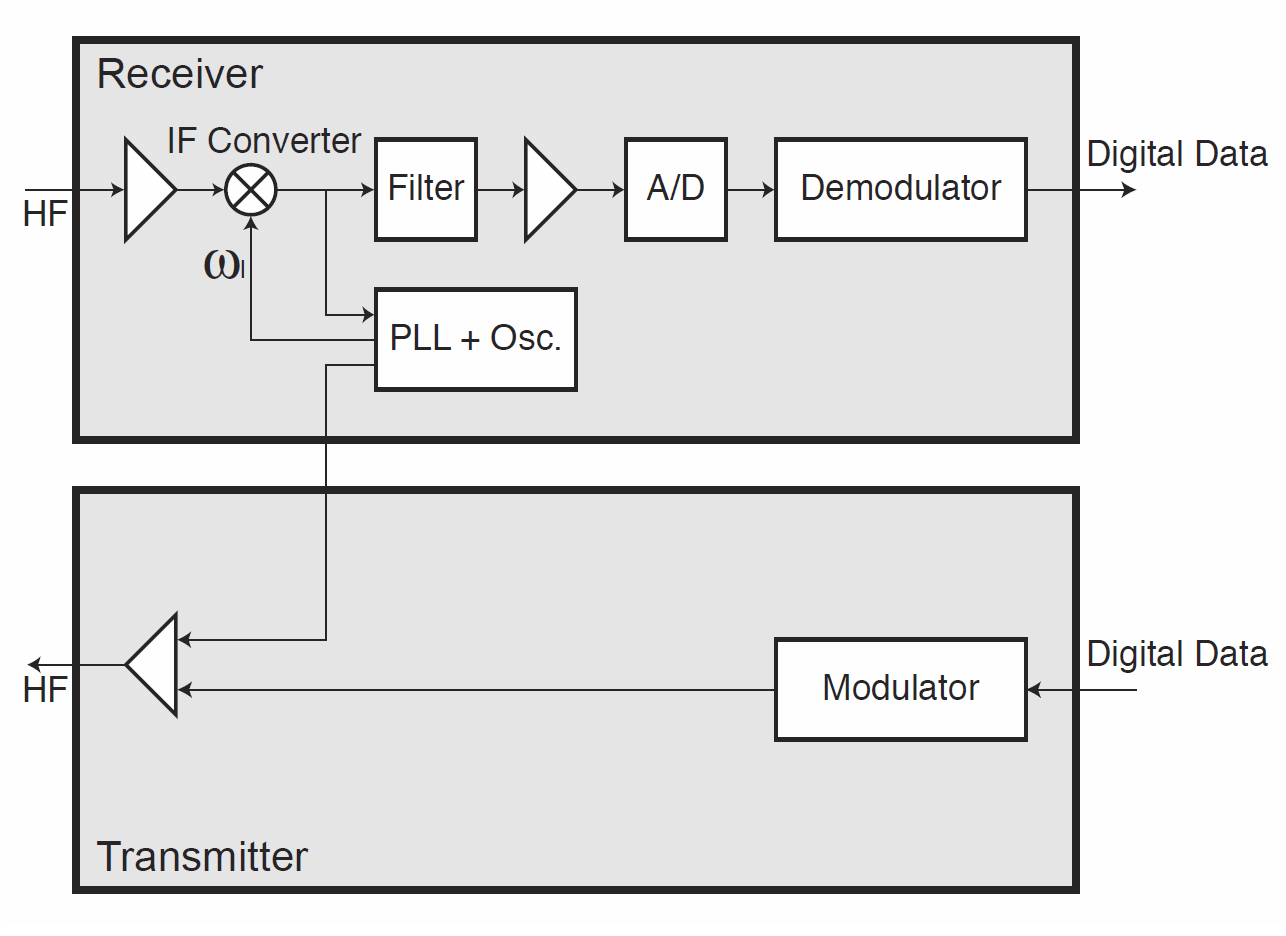

Abb. 1-2 zeigt prinzipiell den Aufbau des CC1020, der dem Aufbau heutiger Transceiver entspricht. Der Empfangsteil (Receiver) des Transceivers verstärkt zunächst das von der Antenne empfangene hochfrequente Signal mittels eines Vorverstärkers. Dies ist notwendig, damit für die weitere Verarbeitung des Signals der Signalpegel möglichst einen Schwellwert nicht unterschreitet und damit eine möglichst fehlerfreie Signalerkennung gewährleistet ist. Da die Signalstärke des hochfrequenten Signals Schwankungen unterliegt, passt sich der Verstärker adaptiv an die Signalstärke an, um möglichst einen konstanten Pegel einzustellen. Das so verstärkte hochfrequente Signal wird anschließend in ein niedrigeres Frequenzband, in die sogenannte "Immediate Frequency (IF)" wI transformiert. Diese Aufgabe erledigt der "IF Konverter". Manchmal wird zusätzlich nicht nur ein Signal der Frequenz wI erzeugt, sondern auch ein Signal mit der quadratischen Frequenz wQ. Hierdurch ist die weitere Verarbeitung des Signals unabhängig von der Trägerfrequenz des hochfrequenten Signals. Dies ist besonders vorteilhaft, wenn sich die Trägerfrequenz variabel einstellen lässt. Die Signalverarbeitung ist bei niedrigen Frequenzen in der Regel einfacher und robuster zu implementieren als bei hohen Frequenzen. So produziert der IF-Empfänger ein geringeres Rauschen als der HF-Empfänger. Das IF-Signal wird anschließend gefiltert und nochmals verstärkt.

Zuletzt wird das gefilterte und verstärkte IF-Signal mit einem A/D-Wandler digitalisiert und steht als binäres Signal nach der digitalen Demodulation zur Verfügung. Sowohl für den Empfänger als auch für den Sender steht ein Oszillator (Osc) zur Verfügung, der in der Regel durch einen externen Quarz angetrieben wird. Der Oszillator erzeugt alle notwendigen Takte für den Empfänger und Sender. Hierfür enthält er Frequenzteiler und Multiplexer, die jeweils den gewünschten Takt zum richtigen Zeitpunkt erzeugen. Für die Synchronisation der Takte an die Taktfrequenz des empfangenen Signals wird in der Regel eine "Phased-Locked Loop, PLL"-Schaltung verwendet. Da die PLL eine zentrale Komponente des Transceivers ist, wird auf sie näher in Kapitel "Zusätliche Literatur" eingegangen. Der Sender (Transmitter) eines Transceiver ist in der Regel sehr einfach aufgebaut. Das binäre Signal wird zunächst moduliert und anschließend einem HF-Verstärker zugeführt.

Der Verstärker ist regelbar, sodass eine gewünschte Sendeleistung eingestellt werden kann. Abschließend wird das so entstandene HF-Signal von der Antenne abgestrahlt.

Der Modulator und Demodulator kann wahlweise verschiedene Modulationen erzeugen. Neben dem "Amplitude Shift Keying (ASK)" oder auch "On Off Keying (OOK)" genannt, beherrscht er "Frequency Shift Keying (FSK)" und "Gaussian FSK (GFSK)". Neben dem Senden und Empfangen von Daten bietet der CC1020 eine Vielzahl von zusätzlichen Funktionen an:

- Leitungscodierung: Das binäre Signal wird einer Kodierung unterzogen, bevor es moduliert wird. An Kodierungen stehen die "Non Return to Zero (NRZ)"- und die Manchester-Kodierung zur Verfügung.

- Scrambling: Zusätzlich kann das binäre Signal durch einen Scrambler verwürfelt werden. Hierdurch wird die Synchronisation (vor allem bei andauernden 0- oder 1-Folgen) beim Empfangssignal erleichtert und ein für die Übertragung günstigeres Spektrum des Signals erreicht.

- Frequenzmultiplex: Die Trägerfrequenz kann im Bereich von 804 MHz bis zu 940 MHz variiert werden. Durch das Frequenzmultiplex können mehrere Transceiver, ohne sich gegenseitig zu stören, betrieben werden. Um die Robustheit einer Übertragung zu erhöhen, können die Transceiver zum Aufbau eines "Frequency Hopping"-Systems verwendet werden.

- Anzeige der Empfangsqualität: Beim Empfang von Daten wird die Empfangsqualität von einem "Receive Signal Strength Indicator (RSSI)" gemessen. Der RSSI dient jedoch nicht nur zur Beurteilung der Empfangsqualität, sondern er kann auch als "Carrier Sense (CS)"-Signal zur Implementierung von Mehrfachzugriffsprotokollen verwendet werden.

2.1.1 RSSI

Das RSSI-Signal dient dazu, die Signalstärke zu ermitteln. Der Wert kann einen Wert von 0 bis 63 annehmen und wird im digitalen Teil des IF-Empfängers gemessen. Da der RSSI mitunter starken Schwankungen unterliegt, wird dieser intern durch den CC1020 über mehrere Messungen gemittelt.

Der Messwert wird nach folgender Gleichung ermittelt:

Als Signalamplitude wird der Wert am Ausgang eines adaptiven Verstärkers verwendet, des "Variable Gain Amplifier (VGA)". Um einen Zusammenhang zwischen dem RSSI und der HF-Leistung PHF herzustellen, kann grob die folgende Gleichung verwendet werden:

In Gl. (1.1) ist die Variable "RSSI" der gemessene RSSI-Wert und KVGA symbolisiert den Verstärkungsfaktor des VGA. Gl. (1.2) ist jedoch unvollständig, weil nicht die frequenzabhängigen Komponenten des CC1020 berücksichtigt werden (z.B. Filter und Verstärker in den Komponenten des Transceivers). Durch sie ergibt sich ein Abweichung des RSSI-Werts RSSIoffset vom realen RSSI-Wert des hochfrequenten Signals an der Antenne. Beispielsweise ergeben sich für unterschiedliche Verstärkungsfaktoren KVGA unterschiedliche RSSI-Werte. Dementsprechend ist dieser RSSIoffset in Gl. (1.2) von PHF abzuziehen. Somit ergibt sich der Zusammenhang zwischen dem RSSI und PHF zu:

Da sich die Berechnung von RSSIoffset aufgrund der Schaltungseigenarten nicht allgemein ausdrücken lässt und darüber hinaus äußerst komplex ist, stellt der Hersteller Messdaten über den Zusammenhang zwischen RSSI und PHF bereit (siehe Datenblatt des CC1020, Seite 34, auf ISIS verfügbar). Der für die Transceiver verwendete Treiber approximiert selbstständig die Eingangsleistung aus den in der obigen Gleichung vorkommenden Parametern.

2.1.2 Schnittstelle zum Mikroprozessor

Die Schnittstelle zum Mikroprozessor bietet die folgenden Funktionen an:

- Abfragen des Controller-Status

- Programmieren des Controllers

- Senden und Empfangen von Daten

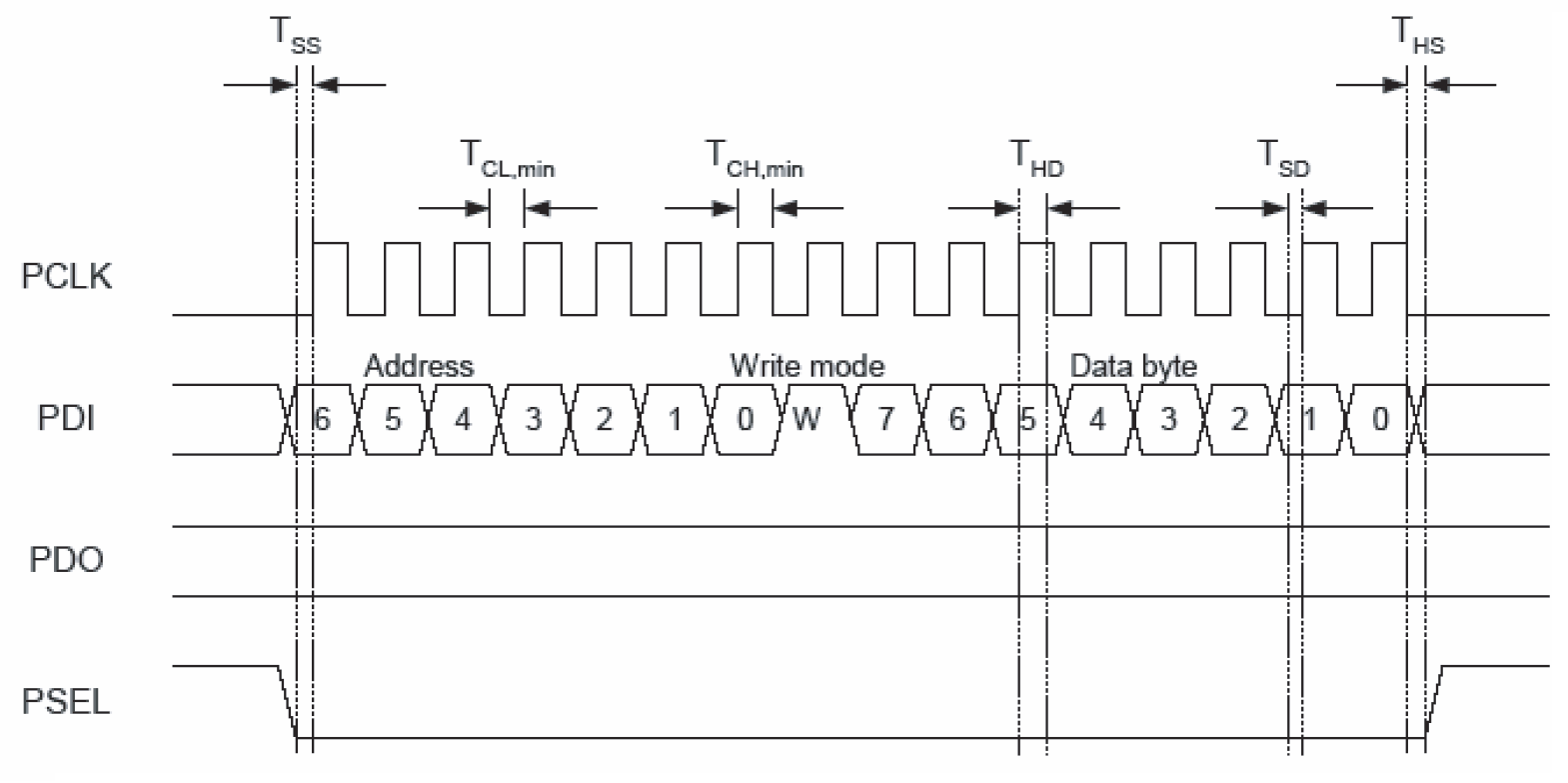

Programmieren des Bausteins

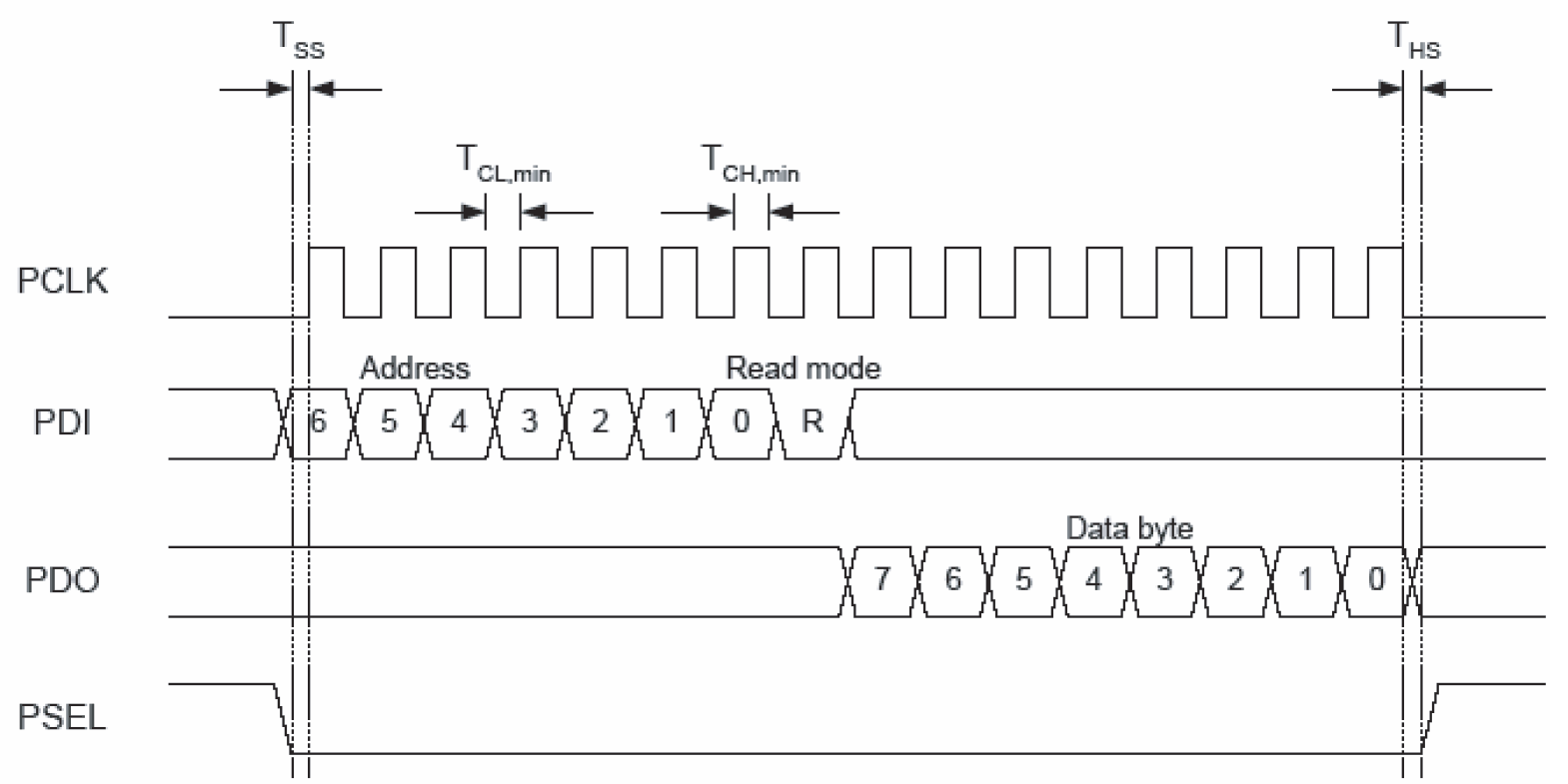

Der CC1020 wird über eine serielle Schnittstelle programmiert. Die serielle Schnittstelle setzt sich aus den Signalen "Programming Select (PSEL)", "Programming Data Input (PDI)" und "Programming Clock (PCLK)" zusammen: Das Signal PSEL dient dazu, dem Transceiver mitzuteilen, dass er programmiert werden soll. Wird das Signal aktiv, muss der Mikroprozessor zuvor ein Taktsignal (PCLK) bereitstellen. An jeder steigenden Flanke von PCLK liest der Transceiver die Daten, die am Signal PDI aktiv sind. Diese zeitliche Abfolge der Signale ist in Abb.1-3 dargestellt.

Abb. 1-3 deutet darüber hinaus an, dass die zu programmierenden Daten eine Semantik besitzen. Um sie zu verstehen, muss man wissen, dass heutige Controller eine Vielzahl von Registern besitzen, deren Werte angeben, welche Funktion des Controllers aktiviert werden soll und welche nicht. Beispielsweise wird über ein Register eingestellt, welche Modulation der CC1020 verwenden soll. Eine ausführliche Beschreibung der Register ist im Datenblatt des CC1020 enthalten. Die Werte der Register können im Praktikum gelesen und geschrieben werden. Bei der Programmierung des Chips muss angegeben werden, welches Register programmiert werden soll. Dies wird mit den ersten 7 Bits des PDI-Signals dem Controller bekannt gegeben. Das 8. Bit muss eine "1" sein. Dies signalisiert, dass Daten in das betreffende Register geschrieben werden. Bei einer "0" wird das entsprechende Register gelesen. Die nachfolgenden 8 Bits geben den Wert an, der in das Register geschrieben bzw. gelesen werden soll.

Abfragen des Controller Status

Der Status des Controllers wird in den internen Registern des Controllers gespeichert. Um den Status des Controllers zu ermitteln, werden die Register mittels der Programmier-Schnittstelle gelesen. In Analogie wird zusätzlich zu den Signalen PSEL, PDI und PCLK das Signal "Programming Data Output (PDO)" verwendet. Wie Abb. 1-4 zeigt, ist das Timing-Diagramm nahezu identisch mit dem Programmieren der Register.

Zuerst wird das Signal PCLK eingeschaltet, anschließend wird mittels der ersten 7 Bit des Signals PDI angegeben, welches Register gelesen werden soll. Auf der Leitung PDO schreibt der Controller die Werte des entsprechenden Registers. Der Mikroprozessor kann an jeder steigenden Flanke des Signals PCLK ein Bit des Registers lesen. Zusätzlich sind einige Controller Status-Informationen direkt über ein Pin des Chips zugänglich. Dies ist immer dann notwendig, wenn Informationen möglichst schnell verfügbar sein sollen und keine Zeit zum Lesen von Registern übrig bleibt. Wegen der niedrigen Datenübertragungsgeschwindigkeit sind solche Status-Pins im CC1020 kaum notwendig. Lediglich für Testzwecke ist das Pin LOCK verfügbar. Es zeigt an, ob die PLL sich synchronisiert hat oder nicht.

Senden und Empfangen von Daten

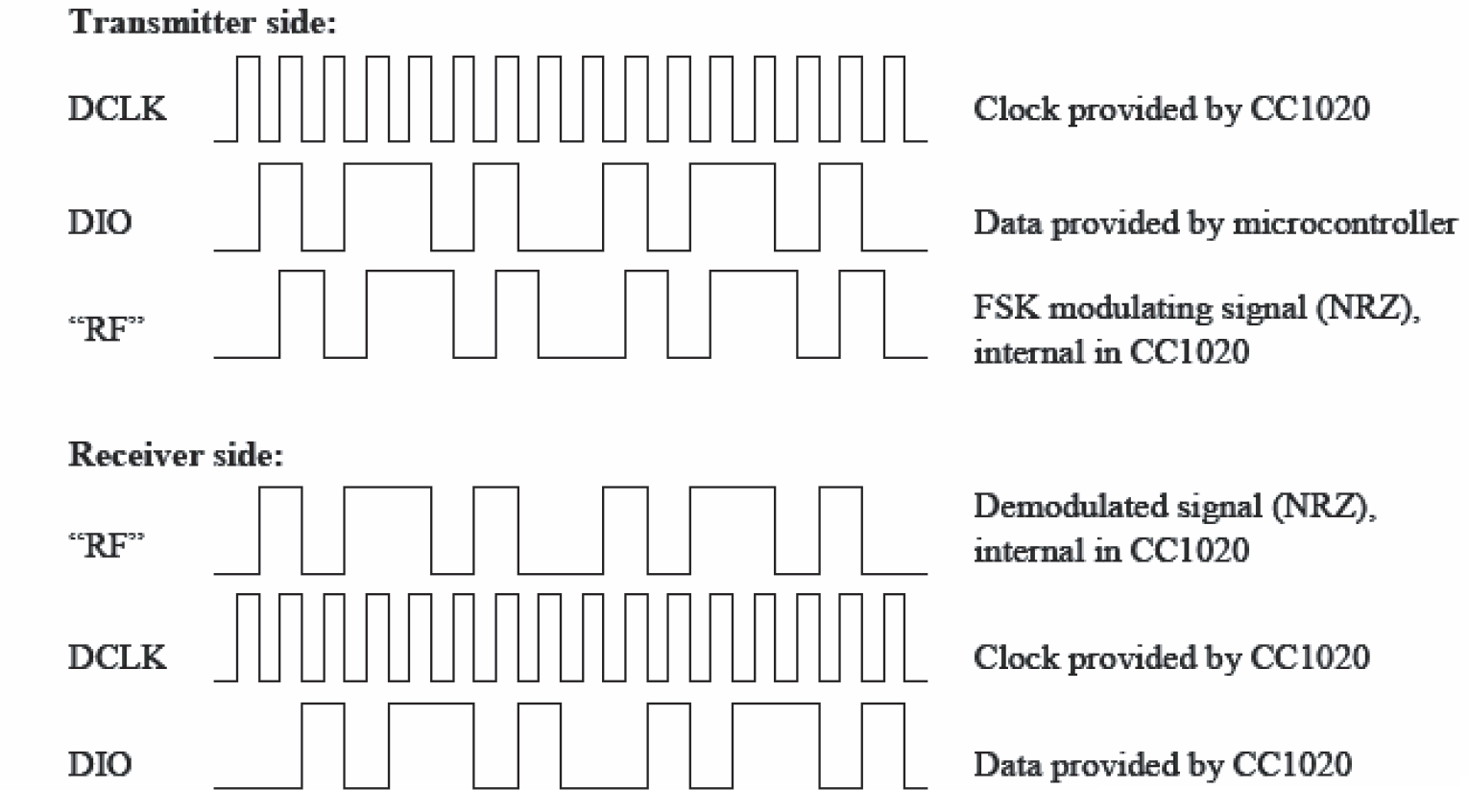

Nachdem der Controller initialisiert wurde, kann er Daten senden oder empfangen. Der Controller kann nicht gleichzeitig Daten senden und empfangen. Mittels der Programmierschnittstelle wird er in den Empfangs- oder Sendemodus geschaltet. Die Datenübergabe an den Controller erfolgt über eine serielle Schnittstelle. Die serielle Schnittstelle besteht aus den Signalen "Data Clock (DCLK)" und "Data Input/Output (DIO)". Das Signal DCLK wird vom Controller bereitgestellt. Bei einer positiven Flanke des Signals DCLK kann der Mikroprozessor empfangene Daten übernehmen, die der Controller am Signal DIO bereitgestellt hat. In Analogie hierzu werden vom Controller bei einer steigenden Flanke des DCLK Daten gesendet, die der Mikroprozessor am Signal DIO bereitgestellt hat. Dieses Prozedere ist grafisch in Abb. 1-5 dargestellt.

2.1.3 Kodierung

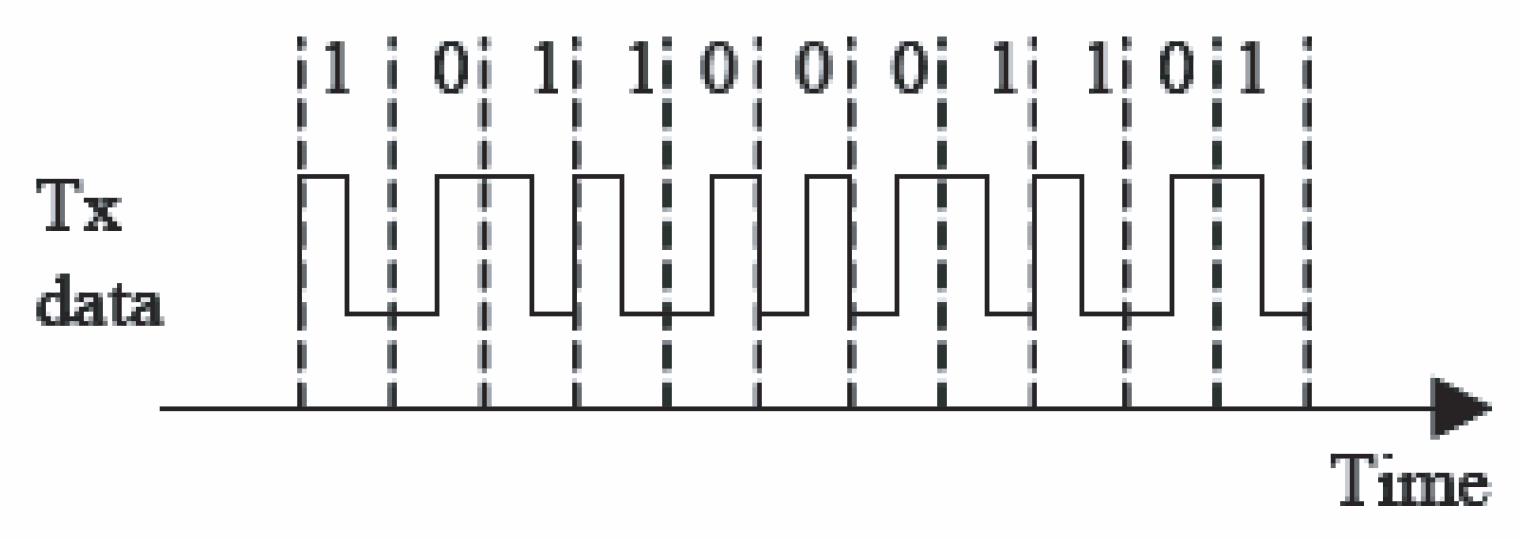

Wie in Abb. 1-5 dargestellt, sendet der CC1020 die Daten NRZ-codiert zum Empfänger. Diese Art der Datenübertragung hat einen Nachteil. Die Synchronisation am Empfänger wird erschwert, wenn die Daten hauptsächlich aus "Nullen" oder Einsen bestehen, also keine Änderungen im Signalpegel erkennbar sind. Aus diesem Grund bietet der Controller die Möglichkeit an, dass die Daten vor dem Senden in die Manchester-Kodierung umgewandelt werden und am Empfänger von der Manchester-Kodierung wieder in die NRZ-Kodierung gewandelt werden. Die Vorschrift der Manchester-Kodierung besagt, dass eine binäre "0" durch den Wechsel von einem Signal mit einem "Null"-Pegel gefolgt von einem Signal mit einem "1"-Pegel codiert wird. In Analogie wird eine logische "1" durch einen Wechsel eines Signals mit einem "1"-Pegel gefolgt von einem Signal mit einem "0"-Pegel codiert. Wie in Abb. 1-6 zu erkennen ist, erfolgt bei jedem zu sendenden Bit ein Pegelwechsel. Insofern detektiert der Empfänger die Pegelwechsel von einem "0"- zu einem "1"-Pegel bzw. von einem "1"- zu "0"-Pegel. Die Synchronisation zwischen Sender und Empfänger wird erheblich erleichtert.

2.1.4 Scrambling

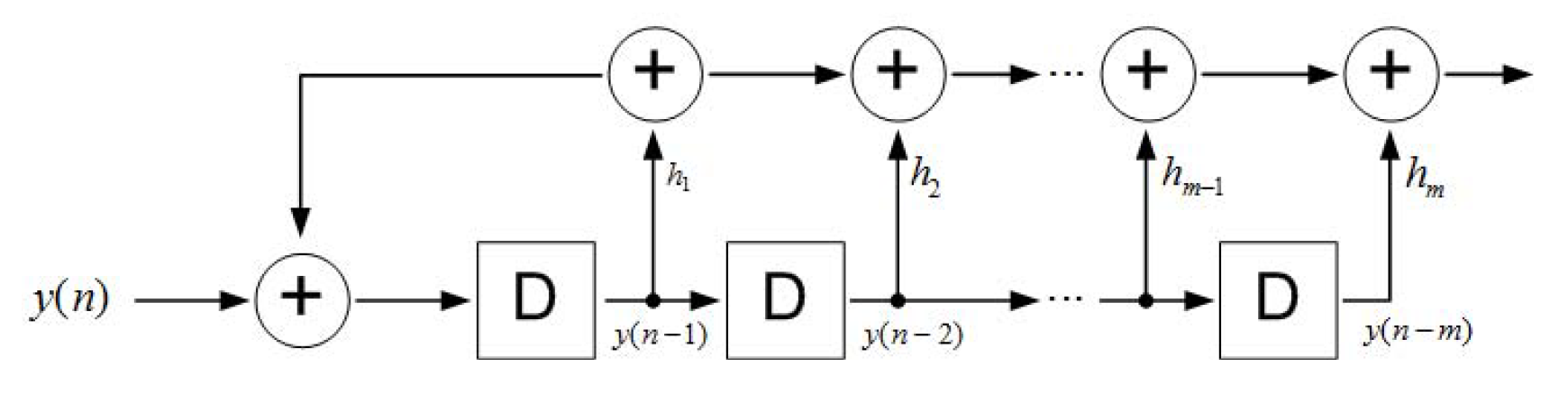

"Scrambling" bezeichnet den Vorgang des "Verwürfelns" von Daten. Dies hat hauptsächlich den Zweck, binäre Folgen zu erzeugen, die möglichst keine aufeinanderfolgende identische - "0"- oder "1"-Signale - enthalten. Um Daten zu "scramblen", werden "Pseudo Noise, (PN)"-Sequenzen generiert. Wie in Abb. 1-7 dargestellt, wird eine solche Zufallsfolge durch Rückkopplungen des zu sendenden Signals mit Hilfe eines Schieberegisters erzeugt.

Gl. (1.4) beschreibt das Verhalten des Scramblers. Zu sendende binäre Daten werden nach jedem Takt in ein Schieberegister geschoben. Die Ausgänge D des Schieberegisters werden mittels "XOR"-Verknüpfungen mit dem Eingang des Schieberegisters multipliziert. Die Koeffizienten \(h(k)\) entsprechen entweder der Multiplikation mit "1" oder mit "0". Insofern beschreiben die Koeffizienten \(h(k)\) einen Polynom der Ordnung m. Je größer m ist, desto größer wird die PN-Folge und desto geringer ihre Autokorrelation. Beispielsweise verwendet der CC1020 das Polynom \(x^9+x^5+1\). Damit die Ordnung m sofort erkennbar ist, werden die Folgen \(PN_m\) bezeichnet. Die PN-Folge des CC1020 wird dementsprechend \(PN_9\)-Folge genannt.